# A DC to 38-GHz Distributed Analog Multiplier Using InP HEMT's

Yuhki Imai, *Member, IEEE*, Shunji Kimura, *Member, IEEE*,

Yohtaro Umeda, *Member, IEEE*, and Takatomo Enoki, *Member, IEEE*

**Abstract**—A novel distributed analog multiplier is proposed. It employs Gilbert cells as the unit section of the distributed structure. The single-ended analog multiplier MMIC's are built using 0.1- $\mu$ m-gate-length InP HEMT's and uniplanar technology. The conversion gain is about -5 dB with LO power of 10 dBm. RF and IF 3-dB bandwidths are 38 and 16 GHz, respectively.

## I. INTRODUCTION

**G**ILOBERT-CELL-BASED analog multipliers are widely used as active double-balanced mixers in microwave applications (1). They are also the key components for high-bit-rate coherent optical heterodyne receivers in lightwave applications. Compared with conventional diode mixers, active mixers have advantages such as a positive conversion gain and good VSWR's for all ports. However, its wideband characteristics are severely limited by transistor performance. The best reported results are around 20 GHz, even when high-cutoff-frequency HBT devices are used [2], [3].

Distributed design is one way to obtain a wide bandwidth with less transistor-performance sensitivity. The use of a distributed structure for active FET mixers has already shown its advantages over conventional ones [4], [5]. However, previous works are only a simple extension of the distributed amplification concept because they used structures similar to distributed amplifiers. It is still questionable whether the distributed structure can be applied to more complicated circuits.

In this letter, we propose a new distributed analog multiplier using Gilbert cells as the unit sections. The MMIC's are fabricated using InP HEMT and uniplanar technology. They show a DC to 40-GHz bandwidth and demonstrate the design advance of the distributed structure for the analog multiplier.

## II. CIRCUIT DESIGN

The distributed mixers reported so far have usually used single-gate common-source FET's or dual-gate common-source FET's as the unit sections. RF and LO signals are fed to the gate terminal while an IF signal is extracted from the drain terminal for the single-gate mixer. On the other hand, RF and LO signals are separately fed to the first and second gate terminals for the dual-gate mixer. Artificial transmission lines are formed at the gate and drain terminals by high-impedance transmission lines and time-averaged FET impedances.

Manuscript received July 16, 1994.

The authors are with NTT LSI Laboratories, Kanagawa, 243-01, Japan.

IEEE Log Number 9406376.

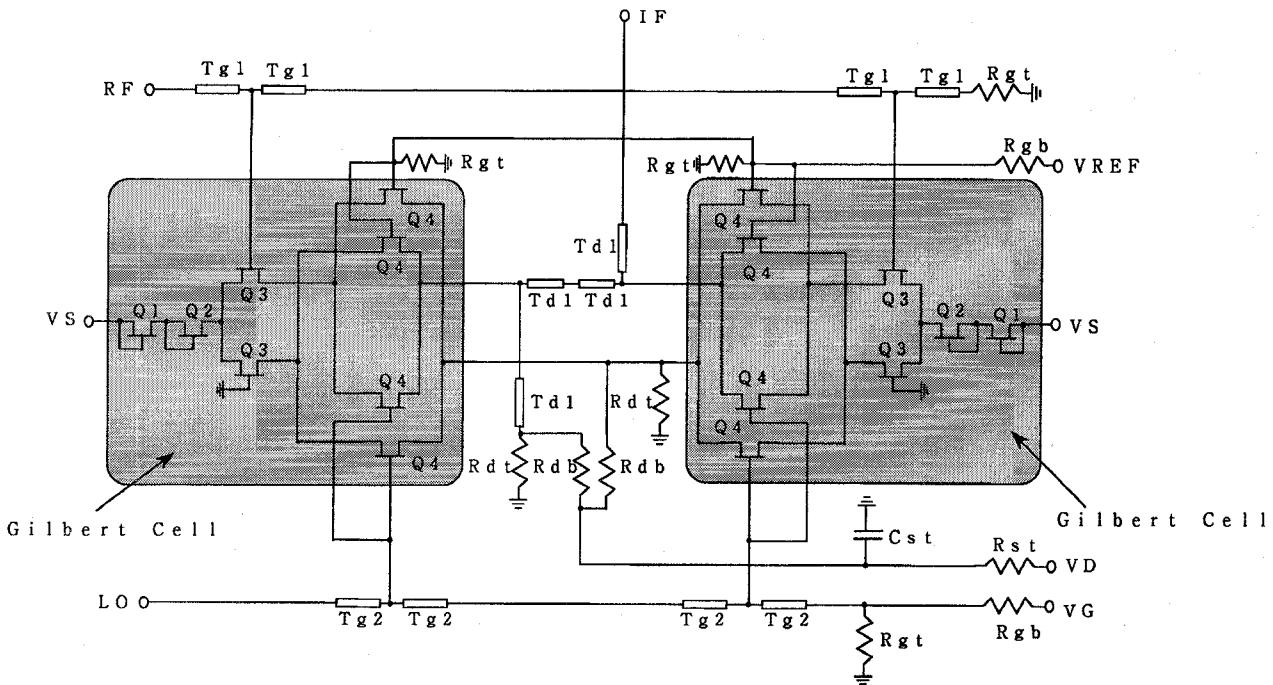

A distributed analog multiplier employs a completely different structure because the unit sections are Gilbert cells. Fig. 1 shows a schematic diagram of our 2-section distributed analog multiplier with a single-ended configuration. FET's Q1–Q4 form a Gilbert cell for the distributed-structure unit section. RF and LO signals are separately fed to the gate terminals of Q3 and Q4 while an IF signal is extracted from the drain terminal of Q4. RF and LO artificial transmission lines are formed by high-impedance transmission lines ( $T_{g1}$  and  $T_{g2}$ ) and input impedances of Q3 and Q4. These artificial lines provide the wideband matching for the RF and LO signals. These lines are designed to have equal phase shifts between the unit sections as in conventional distributed mixers. An IF artificial transmission line is formed by a high-impedance transmission line ( $T_{d1}$ ) and output impedance of Q4. The IF artificial line is necessary, especially for a up-converted signal. It is noteworthy that a small-signal input impedance can be used in the artificial-line design as it is in distributed-amplifier design. This is because FET's nonlinearity is not used, and it operates in the linear region for the analog multiplier. To insure the operation from DC frequency, the termination resistors ( $R_{gt}$  and  $R_{dt}$ ) are directly connected to DC grounds. For the gate biases, a large resistor ( $R_{gb}$ ) eliminates the effect of external inductances on the high-frequency performance. For the drain bias, a resistor-capacitor biasing network ( $R_{db}$ ,  $R_{st}$  and  $C_{st}$ ) is employed instead of a large resistor to reduce the supply voltage.

Detailed design was done with a harmonic balance simulator using a HEMT model with  $f_T = 155$  GHz and  $gm_0 = 1.4$  S/mm. Gate widths of Q1 and Q2 are 200  $\mu$ m, and Q3 and Q4 are 100 and 50  $\mu$ m, respectively. The impedance of the high-impedance transmission line is 75 ohm. The designed performance is about a -8-dB conversion gain and a 50-GHz 3-dB RF bandwidth with a 0-dBm LO power and a 1-GHz IF frequency for the single-ended configuration shown in Fig. 1. Although the single-ended configuration is adopted in this work, a complete double-balanced mixer could be easily constructed in an MMIC format by using a passive balun or a distributed active balun.

## III. FABRICATION

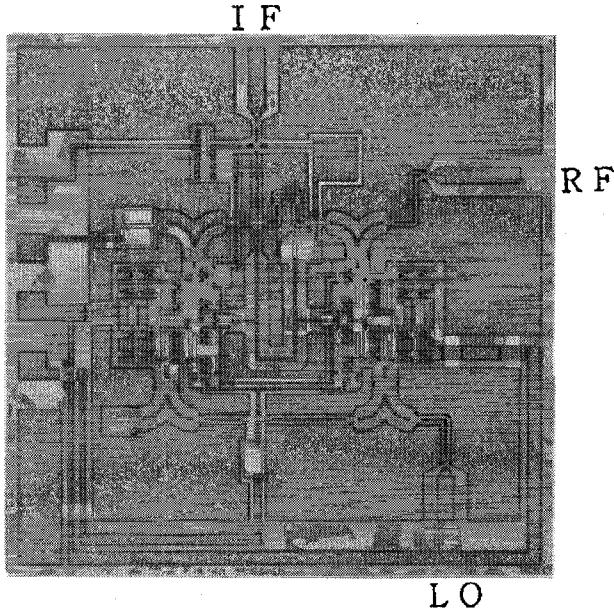

MMIC's were fabricated using InAlAs/InGaAs/InP HEMT's with a gate length of 0.1  $\mu$ m [6]. The transmission line is a coplanar waveguide. A microphotograph of an MMIC is shown in Fig. 2. Chip size is 2  $\times$  2 mm.

Fig. 1. Schematic diagram of the 2-section distributed analog multiplier with a single-ended configuration.

Fig. 2. Microphotograph of distributed analog multiplier MMIC.

#### IV. PERFORMANCE

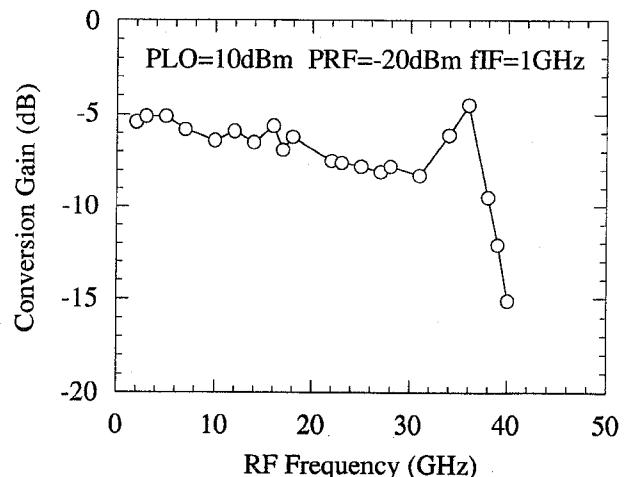

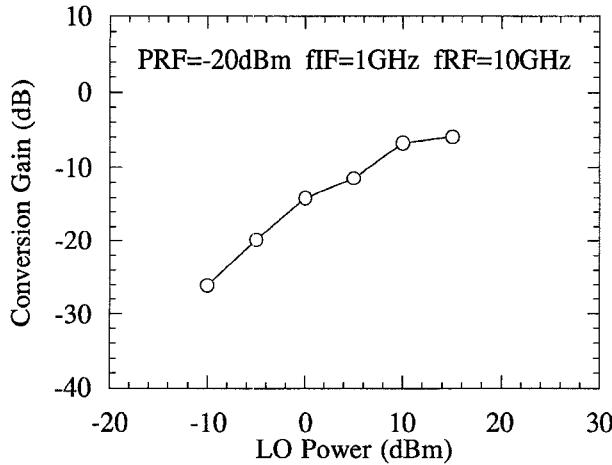

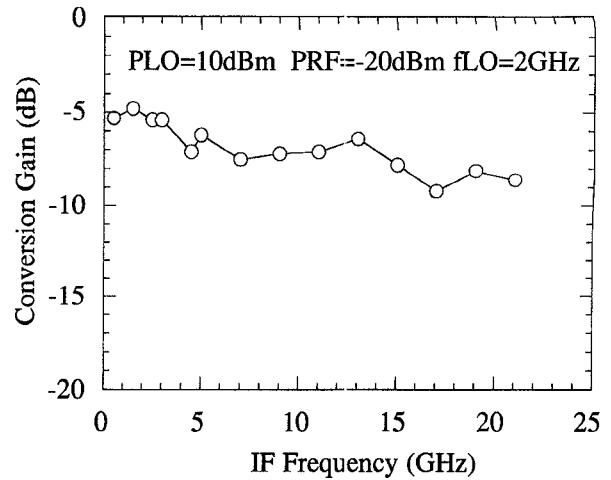

MMIC's were measured using on-wafer probes. The conversion gain was measured at  $-20\text{-dBm}$  RF power. Fig. 3 shows the conversion gain as a function of RF frequency with IF frequency of  $1\text{ GHz}$  and LO power of  $10\text{ dBm}$ . The conversion gain was about  $-5\text{ dB}$  with a 3-dB RF bandwidth of about  $38\text{ GHz}$ . DC power consumption was about  $2.5\text{ W}$ . Fig. 4 shows the conversion gain versus the power level of LO power. IF and RF frequencies are  $10\text{ GHz}$  and  $1\text{ GHz}$ , respectively. The conversion gain almost saturated around  $10\text{ dBm}$  of LO power. The conversion gain was lower than designed because the transconductance decreased more than expected. Fig. 5 shows

Fig. 3. Conversion gain as a function of RF frequency.

the conversion gain as a function of IF frequency with LO frequency of  $2\text{ GHz}$  and LO power of  $10\text{ dBm}$ . The 3-dB IF bandwidth was about  $16\text{ GHz}$ . RF and LO return losses were better than  $-10\text{ dB}$  in the frequency range below  $30\text{ GHz}$ . Isolations were measured in RF and LO frequency ranges below  $26\text{ GHz}$ . LO to RF isolation was better than  $25\text{ dB}$ . RF to IF and LO to IF isolations were better than  $10\text{ dB}$ . The conversion gain and isolations will be improved by using a double-balanced configuration. The decrease in bandwidth is larger than designed partly because of the extra transmission-line length. This layout restriction was caused by the relatively large area occupied by the unit sections. It will be avoided by reducing the device sizes. This also will reduce the total chip size.

#### V. CONCLUSION

A novel distributed analog multiplier has been proposed. It employs a Gilbert cell as the unit section of the distributed

Fig. 4. Conversion gain as a function of LO power.

structure. Single-ended analog multiplier MMIC's were built using  $0.1\text{-}\mu\text{m}$ -gate-length InP HEMT's and uniplanar technology. The conversion gain is about  $-5$  dB with LO power of  $10$  dBm. RF and IF 3-dB bandwidths are  $38$  and  $16$  GHz, respectively. We believe these bandwidths are the widest ever reported for analog multipliers. Considering its impressive wideband performance, the proposed design technique should have a considerable impact on microwave and lightwave applications.

#### ACKNOWLEDGMENT

The authors wish to thank Y. Akazawa and Y. Ishii for helpful discussions. They also thank S. Horiguchi and T. Mizutani for their encouragement.

Fig. 5. Conversion gain as a function of IF frequency.

#### REFERENCES

- [1] K. J. Negus and J. N. Wholey, "Multifunction silicon MMIC's for frequency conversion applications," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 1191-1198, Sept. 1990.

- [2] K. Osafune and Y. Yamauchi, "20-GHz 5-dB-gain analog multipliers with AlGaAs/GaAs HBT's," *IEEE Trans. Microwave Theory Tech.*, vol. 42, pp. 518-519, Mar. 1994.

- [3] L. M. Burns, J. F. Jensen, W. E. Stanchina, R. A. Metzger, and Y. K. Allen, "DC-to-Ku-band MMIC InP HBT double-balanced active mixer," in *Proc. IEEE Int. Solid-State Circuits Conf.*, 1991, pp. 124-125.

- [4] W. Titus and M. Miller, "2-26 GHz MMIC frequency converter," in *Proc. GaAs IC Symp.*, pp. 181-184, 1988.

- [5] R. Majidi-Ahy, C. Nishimoto, J. Russel, W. Ou, S. Bandy, and G. Zdasiuk, "23-40 GHz InP HEMT MMIC distributed mixer," *IEEE MTT Symp. Dig.*, pp. 1063-1066, 1992.

- [6] Y. Umeda, T. Enoki, and Y. Ishii, "Sensitivity analysis of 50-GHz MMIC-LNA on gate-recess depth with InAlAs/InGaAs/InP HEMTs," *IEEE MTT Symp. Dig.*, pp. 123-126, 1994.